|

TwojePC.pl © 2001 - 2024

|

|

Piątek 28 maja 2021 |

|

| |

|

ZEN 5 Strix Point w litografii 3nm i z koncepcją big.LITTLE

Autor: Zbyszek | źródło: WccFTech | 18:03 |

(21) |  Obecnie opracowywana przez AMD architektura ZEN 4 doczeka się swojego debiutu rynkowego w postaci procesorów Ryzen o nazwie kodowej Raphael przeznaczonych dla komputerów stacjonarnych, oraz procesorów typu APU o nazwie kodowej Phoenix przeznaczonych dla komputerów przenośnych. Obie serie CPU trafią na rynek za kilkanaście miesięcy, i będą wytwarzane w 5nm litografii od TSMC (poza chipletami I/O w Raphael, które skorzystają z innego procesu produkcji). AMD pracuje też nad architekturą ZEN 5, przeznaczoną dla procesorów mających pojawić się na rynku kilkanaście miesięcy później niż CPU z ZEN 4. Obecnie opracowywana przez AMD architektura ZEN 4 doczeka się swojego debiutu rynkowego w postaci procesorów Ryzen o nazwie kodowej Raphael przeznaczonych dla komputerów stacjonarnych, oraz procesorów typu APU o nazwie kodowej Phoenix przeznaczonych dla komputerów przenośnych. Obie serie CPU trafią na rynek za kilkanaście miesięcy, i będą wytwarzane w 5nm litografii od TSMC (poza chipletami I/O w Raphael, które skorzystają z innego procesu produkcji). AMD pracuje też nad architekturą ZEN 5, przeznaczoną dla procesorów mających pojawić się na rynku kilkanaście miesięcy później niż CPU z ZEN 4.

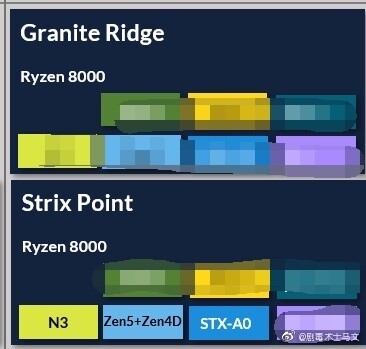

W sieci właśnie pojawiają się pierwsze informacje na ich temat, które mają pochodzić ze źródeł zbliżonych do AMD. Według nich, na bazie ZEN 5 pojawią się CPU o nazwie kodowej Granite Ridge - następcy Ryzenów z serii Raphael, oraz procesory o nazwie kodowej Strix Point, będące następcą APU Rembrandt (ZEN 3 + RDNA 2) i Phoenix (ZEN 4 + RDNA 2). Obie serie procesorów trafią do sprzedaży jako CPU Ryzen serii 8000, i prawdopoodobnie na przełomie 2023 i 2024 roku.

Granite Ridge mają być procesorami przeznaczonymi dla wydajnych desktopów, i będą korzystać z rdzeni x86 z architekturą ZEN 5. Chiplety z tymi rdzeniami będą wytwarzane w litografii 3nm od TSMC. CPU Granite Ridge mają być kompatybilne z podstawką AM5.

Z kolei przeznaczone dla laptopów i energooszczędnych desktopów procesory APU o nazwie kodowej Strix Point, mają skorzystać z koncepcji big.LITTLE, czyli łączenia dużych rdzeni o wysokim wskaźniku IPC z mniejszymi rdzeniami o niższym IPC. Według informacji, procesory te otrzymają miks rdzeni ZEN 5 i ZEN 4D - te ostatnie będą bazować na zmodyfikowanej architekturze ZEN 4, przeniesionej do litografii 3nm i zoptymalizowanej pod kątem mniejszego zużycia energii i mniejszej zajętości powierzchni krzemowej.

Koncepcja big.LITTLE jest od dłuższego czasu obecna w procesorach smartfonowych z architekturą ARM, jednak jeszcze w tym roku pojawi się w procesorach x86 dla laptopów i komputerów PC, w postaci szykowanej przez Intela serii Alder Lake-S. Wygląda na to, że AMD również przygotuje procesory tego typu, które powinny powalczyć z następcami Alder Lake od Intela, czyli zapowiadanymi na 2023 rok procesorami Meteor Lake.

|

| |

|

|

|

|

|

|

|

|

|

|

K O M E N T A R Z E |

|

| |

|

- W AMD widzę nadal potrafią myśleć logicznie (autor: kombajn4 | data: 28/05/21 | godz.: 07:04)

i big.LITTLE trafi tam gdzie ma sens czyli do APU czyli na rynek laptopów i mini PC

- @up (autor: Saturn64 | data: 28/05/21 | godz.: 07:36)

W tej koncepcji jest sens i nadaje się również do desktopów. Wystarczy tylko ją odpowiednio wydajnościowo wyskalować . Jak rozumieć koncepcje słabego rdzenia. Wg. mnie powinien to być obecny mocny rdzeń odpowiednio przeprojektowany by mógł być bardziej energooszczędny przy podobnej lub tej samej wydajności. Natomiast mocne rdzenie powinny być co najmniej 100% wydajniejsze od słabych. Taki procesor dawałby sobie świetnie radę w działaniach single i multi. A obecna koncepcja wszystkich takich samych rdzeni nie mogła by konkurować z procesorami tego typu w działaniach single.

- @2. (autor: Kenjiro | data: 28/05/21 | godz.: 08:52)

Tylko, że to się wiąże z tym, że albo ze słabszych rdzeni zostanie wycięta funkcjonalność (np. skrócony potok, zmniejszona lista predykcji skoków, zmniejszony cache L1), przez co wydajność poleci na pysk przy niewielkim zysku energooszczędności. Zróżnicować rdzeni względem możliwości (np. wyciąć AVX) się nie da, bo wtedy nie przełączysz wątku na słabszy rdzeń, gdyż się wysypie.

W efekcie słabe rdzenie będą musiały być "spuchnięte", aby te mocne nie musiały rezygnować z funkcjonalności, co przynosi słabe rezultaty.

Co innego wersja dla laptopów, tam będzie mógł być procesor w ogóle bez wsparcia AVX, ogólnie obcięty, gdzie słabsze rdzenie zostaną wykastrowane jeszcze bardziej.

Niestety efektem będzie fragmentacja rynku procesorów, gdzie będzie N procesorów o niekompatybilnych możliwościach i soft po prostu na jednych będzie działać, a na drugich nie.

- @up (autor: Saturn64 | data: 28/05/21 | godz.: 09:08)

Jaka jest różnica pomiędzy obecnymi rdzeniami zen3 dla laptopów a do komputerów stacjonarnych oprócz wyższych taktowań?

- @4. (autor: Kenjiro | data: 28/05/21 | godz.: 09:36)

Pi*oko żadna. A w szczegółach oczywiście są różnice, bo to jednak są różne projekty, gdyż rdzenie dla notebooków to monolity, a nie chiplety, więc i cache różny, i kolejki pewnie inne.

Niemniej jednak same możliwości rdzeni Zen powinny być identyczne.

Już samo zmniejszenie taktowania zbija wymaganą energię nawet wielokrotnie. Skomplikowanie budowy rdzeni x86 powoduje, że nie da się tam niewiele wyciąć, by mieć duży zysk. Niestety, trzeba jak w RISCach, uprościć na maxa i dopiero wtedy jest zysk energetyczny, niestety wydajność wtedy też generalnie leży i kwiczy (nawet 4 GHz RISC-V jest daleko od podobnie taktowanego x86).

- @04 (autor: kombajn4 | data: 28/05/21 | godz.: 09:46)

Mają całkowicie inną budowę No dobra prawie całkowicie bloki CCX są do siebie zbliżone.

@Kenjiro

Ty myślisz jak zrobić tak zeby przy zadaniach wymagających maksymalnej wydajności móc używać wszystkich dostępnych rdzeni. Moim zdaniem wcale nie trzeba się bawić w takie zabiegi. Można usunąć np AVX z małych rdzeni i zastosować flagi - program odwołuje się do danych instrukcji odpalamy go wyłącznie na bloku dużych rdzeni. To trzeba by załatwić po stronie systemu operacyjnego więc pewnie ewangeliści rupiecia pt Win 7 by się obrazili.

Jest jeden warunek żeby to miało ręce i nogi konfiguracja z 2 no maksymalnie 4 małymi rdzenia (do przeglądarki, poczty i YT starczy) a cała reszta CPU w postaci dużych rdzeni - wtedy przy wymagających obliczeniach możesz po prostu pominąć małe rdzenie. I generalnie zamiast bawić się w łączenie dwóch (odmiennych i przeznaczonych do różnych celów) rodzajów rdzeni do wspólnej pracy po prostu przełączać CPU z jednego bloku na drugi. Ko

Tak czy inaczej na desktopie jest to poroniony pomysł i zdecydowanie lepszym rozwiązaniem są same wydajne rdzenie o dużym zakresie dostępnych częstotliwości pracy.

- @6. (autor: Mariosti | data: 28/05/21 | godz.: 10:52)

Zgaduję że bardzo duży zysk energooszczędności będzie wtedy kiedy po prostu przeniosą Zen4 do 3nm, a rdzenie Zen5 będą całkowicie wyłączalne, wraz z ich cache.

Wtedy zasadniczo wystarczy że Zen5 będzie miał wsparcie dla AVX512 i więcej różnic nie potrzeba. No i te grube rdzenie nie muszą być 100% wydajniejsze. Wystarczy że będą 15-20% wydajniejsze w większości zastosowań, a np tam gdzie potrzebne będzie bardzo mocne FPU albo ten szeroki AVX, to tam faktycznie będą mogły uzyskać 50-100% lepsze wyniki. Przy okazji, zakładając że do wszelkich niższych stanów energetycznych używane byłyby rdzenie Zen4, rdzenie Zen5 mogłyby być potencjalnie nieco uproszczone pod kątem oszczędzania energii właśnie, bo nie musiałyby obsługiwać sprzętowo aż tak wielkiej gradacji stanów energetycznych jak obecne rdzenie.

- odnosze wrażenie (autor: Mario2k | data: 28/05/21 | godz.: 18:39)

że co najmniej kilku z was robi przy produkcji CPU w Intelu albo AMD . Prawda chyba zgoła odmienna , bujamy bujamy na maksa bujamy w obłokach .

- @up (autor: Saturn64 | data: 28/05/21 | godz.: 21:11)

Wiem jakie są różnice pomiędzy rdzeniami Zen3 dla laptopów a desktopami. Było to pytanie, które miało odpowiedzieć, że architektura jest ta sama a jednak jedne rdzenie mogą być energooszczędne a drugie nie. Wszystko zależy od ich taktowania. Koncepcji w tego typu może być wiele i mogą dać słabe rezultaty ale też mogą być dobre gdy odpiwiednio się je rozwinie.

1. Kilka słabych rdzeni energooszczędnych i dużo mocnych używanych tylko podczas obciążenia. (nadaje się bardziej do leptopa)

2. Dużo rdzeni mocnych i kilka super mocnych. (do desktopa)

3. Różnicowanie rdzeni w kwestii obsługi danych rozkazów (ta koncepcja jest mi się wydaje najtrudniejsza do implementacji)

- Tu najważniejsza jest kwestia poboru w IDLE (autor: ekspert_IT | data: 28/05/21 | godz.: 21:50)

Konieczna jest poprawa agresywnego taktowania. Jak się wpisze frazę IDLE high frequency CPU to wyskoczą setki tysięcy wyników dla różnych procesorów intela i AMD stwierdzające, że nawet w planie 'balanced power' często procesory chodzą na najwyższych obrotach (przy Wordzie i PDF Foxit Readerze...) - pobierając masę prądu bez sensu. Zamiast ładować nowe małowydajne i małoprądożerne rdzenie, lepiej w mojej opinii AMD i Intel powinny popracować ściśle z Microsoftem co do kwestii zasilania i konieczności aktywnego zbijania taktowania w spoczynku. Spadek z 4Ghz do 500Mhz powinien powodować gigantyczne oszczędności prądu...

- @ Satrun64 i cała reszta (autor: Zbyszek.J | data: 28/05/21 | godz.: 22:30)

różnica miedzy ZEN3 w APU a ZEN3 z desktopowym Vermeer jest najdokładniej żadna, poza o połowę mniejszym cache L3. Nieco inne są też algorytm zarządzania taktowaniem i poborem energii, ale one nie zależą od budowy fizycznej rdzeni. Ta jest taka sama czy to ZEN 3 w APU czy w CPU.

- @11 (autor: kombajn4 | data: 29/05/21 | godz.: 04:22)

Oraz taki drobiazg że APU ma budowę monolityczną podczas gdy CPU desktopowe modułową wytwarzaną w dwóch różnych litografiach. No i APU ma ograniczoną ilość linii PCI-E. Nie no faktycznie zero różnic.... Że już nie wspomnę że często wersja mobilna ma usprawnione rdzenie względem pierwowzoru. Tak było w przypadku Ryzena 2400G który był gdzieś pomiędzy ZEN i ZEN+

- Saturn64 (autor: Markizy | data: 29/05/21 | godz.: 07:36)

3. myślę że za bardo to utrudniasz. W mojej opinii wystarczy dobrze zorganizowany kompilator oraz system zarządzania watkami w OS. Ten pierwszy na etapie kompilacji powinien już umieć wyróżnić watki które wymagają dużej wydajności i te które tego nie potrzebują generując odpowiedni znaczni dla OS, ale to rozwiązanie na przyszłość. Obecnie to windows powinien mieć możliwość monitorowania wykorzystania zasobów przez watek/aplikacja jak wykryje ze duża cześć zasobów jest nie wykorzystana przerzucić go na słabszy rdzeń a mocniejszy wygasić.

Lista rozkazów nie jest tutaj dużym problem bo do dziś wiele aplikacji nie korzysta z avx (jako przykład), a dwa nawet procesory które nie posiadają tych instrukcji potrafią liczyć obliczenia które je wykorzystują, tylko wolniej. Wiec sumarycznie nie jest to tak duży problem bo aplikacja potrafi rozpoznać jakie instrukcje sa wspierane, trzeba tylko sprawdzić i ewentualnie opracować mechanizm na sytuacje jeśli te instrukcję się pojawią lub znikną.

Co do rdzeni słabszych można wykorzystać zmniejszone rdzenie Zen1 i zen 2 bo zakładam że więcej niż 4 rdzenie nie będzie dodawanych jako słabsze. A te rdzenie byłyby wyjątkowo małe już 5 czy nawet 3nm.

- @ kombajn (autor: Zbyszek.J | data: 29/05/21 | godz.: 23:22)

" taki drobiazg że APU ma budowę monolityczną podczas gdy CPU desktopowe modułową wytwarzaną w dwóch różnych litografiach"

Cholera - a jakie to ma znaczenie dla budowy rdzeni ZEN 3 ? Żadne. One są takie same czy to w desktopowym Vermeer czy to w APU, za wyjątkiem cache L3 które mają mniejsze o połowę w APU

- Zbyszek.J (autor: kombajn4 | data: 30/05/21 | godz.: 09:52)

"Cholera - a jakie to ma znaczenie dla budowy rdzeni ZEN 3 " HAHAHAHAHAHAHAHAHAHAH

Sorry nie mogłem inaczej. A jakie znaczenie ma opóźnienie komunikacji pomiędzy chipletami oraz chipletami i modułem I/O za pośrednictwem Infinity Fabric dla wydajności? A wiesz co jest w APU? Monolityczny procesor bez interkonektorów po IF. Dlatego APU z dużo mniejszą pamięcią podręczna nie odstaje od desktopowego Ryzena

- Taka ciekawostka (autor: piwo1 | data: 30/05/21 | godz.: 11:07)

https://www.ixbt.com/...l-56-amd-128-cpu-epyc.html

- kombajn4 (autor: Markizy | data: 30/05/21 | godz.: 14:18)

IF ma znaczenie głównie w grach i programach mocno polegających na przepustowości pamięci cache i ram.

Natomiast sama budowa rdzenia jest identyczna poza obudową peryferiów. Ale i to do czasu bo sam przewiduje że apu na zen4 dostanie IF i osobny chiplet do I/O

@piwo1

symulacja oparta o nadchodzącą wielkość podstawki serwerowej. Niemniej jednak wątpliwe jest żeby AMD kleiło aż 17 układów do PCB. Bardziej prawdopodobne jest zwiększenie ilości rdzeni w chiplecie z 8 do 16 i zostanie przy 9 układach.

- ... (autor: pwil2 | data: 30/05/21 | godz.: 21:53)

Intel idzie w bigLITTLE, bo musi. AMD jest hojnie obdarzone, ale musi ciąć, by nie być gorszym.

http://dowcipy.autentyki.pl/2590

- c.d. (autor: pwil2 | data: 30/05/21 | godz.: 21:54)

Jedno co mogliby zrobić i miałoby jakiś sens to wrzucenie jakichś małych rdzeni do części IOD, a wydajne zostawić w CCD. W idle chiplety mogłyby być odcięte od zasilania, a wybudzałyby się te skromne.

- c.d. (autor: pwil2 | data: 30/05/21 | godz.: 21:56)

W czasie, gdy użytkownik nie jest zalogowany, wszelkie aktualizacje, synchronizacje, backupy mogłyby sobie kapać w tle na tych słabych rdzeniach.

- c.d. (autor: pwil2 | data: 30/05/21 | godz.: 21:57)

Przeglądarka internetowa na słabych rdzeniach? Bez sensu. Nawet Chrome jest ograniczany przez jeden wątek główny przeglądarki i przy większej ilości zakładek potrafi być wąskim gardłem nawet na mocnym procesorze.

|

|

|

|

|

|

|

|

|

D O D A J K O M E N T A R Z |

|

| |

|

Aby dodawać komentarze, należy się wpierw zarejestrować, ewentualnie jeśli posiadasz już swoje konto, należy się zalogować.

|

|

|

|

|

|

|

|

|

|