Test Sandy Bridge: Intel Core i7 2600K

Autor: DYD & Zbyszek | Data: 03/01/11

|

Oficjalna premiera głośno zapowiadanej nowej architektury Intela bez zmian 5 stycznia, a wraz z nią cały pakiet nowych procesorów (zarówno desktopowych jak i mobilnych) oraz chipsetów szóstej serii. Już teraz nastąpiła możliwość podzielenia się publicznie z nową technologią i wydajnością jaką za sobą niesie architektura Sandy Bridge. W artykule sprawdzimy wydajność procesora Intel Core i7 2600K, jego potencjał przy podkręcaniu, pobór mocy, a także nowy zintegrowany układ graficzny zaszyty w CPU. Jak się wyrobimy będzie także cześć teoretyczna. [aktualizacja: teoria już w pełni gotowa, zapraszamy do lektury] Oficjalna premiera głośno zapowiadanej nowej architektury Intela bez zmian 5 stycznia, a wraz z nią cały pakiet nowych procesorów (zarówno desktopowych jak i mobilnych) oraz chipsetów szóstej serii. Już teraz nastąpiła możliwość podzielenia się publicznie z nową technologią i wydajnością jaką za sobą niesie architektura Sandy Bridge. W artykule sprawdzimy wydajność procesora Intel Core i7 2600K, jego potencjał przy podkręcaniu, pobór mocy, a także nowy zintegrowany układ graficzny zaszyty w CPU. Jak się wyrobimy będzie także cześć teoretyczna. [aktualizacja: teoria już w pełni gotowa, zapraszamy do lektury] | |

|

Nowa architektura: część teoretyczna

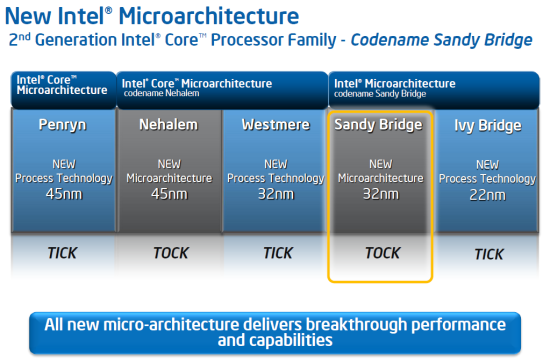

Wraz z wprowadzeniem Core 2 Duo w 2006 roku Intel zapoczątkował strategię Tik-Tak, polegającą na rozwoju procesorów w rytm tykania zegara. Jej podstawowym założeniem jest oddzielenie procesu wprowadzania nowej architektury procesorów, od rozpoczęcia produkcji układów w nowym wymiarze technologicznym. Oba zadania stanowią poważne wyzwanie dla inżynierów a wprowadzane jednocześnie mogą stać się przyczyną dodatkowych problemów i opóźnień.

Zdecydowano więc, że lepiej wprowadzać je niezależnie od siebie, w krótkich i systematycznych odstępach czasu. W efekcie w latach, na które przypada faza „tik” Intel wprowadza nowy proces technologiczny, natomiast w kolejnym roku w fazie „tak” wprowadzana jest nowa architektura.

Tak właśnie powstała strategia Tik-Tak, której kolejnym efektem są debiutujące właśnie dziś, nowe procesory z architekturą Sandy Bridge.

Co zmieniono w Sandy Bridge w porównaniu do wcześniejszych układów z architekturą Nehalem/Westmere? Generalnie rzecz biorąc bardzo wiele. O tym dalej.

Zintegrowany układ graficzny i nowa organizacja procesora

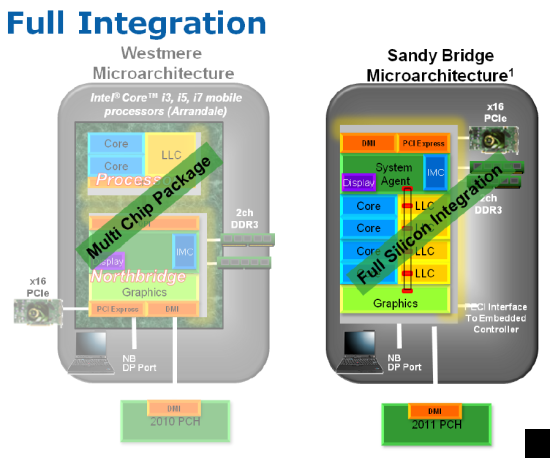

Z technicznego punktu widzenia najważniejszymi zmianami wprowadzonymi w architekturze Sandy Bridge wydaje się być nowa, w pełni modułowa organizacja procesorów oraz integracja układu graficznego wewnątrz nich, w tej samej strukturze krzemowej.

Szczególnie druga z tych zmian jest bardzo istotna - wcześniejsze procesory Core i3/i5 (nazwa kodowa Westmere) ze starszą architekturą Nehalem co prawda miały zintegrowany układ graficzny, jednak umieszczony nie w rdzeniu procesora, ale w oddzielnej 45-nanometrowej strukturze krzemowej na tej samej podstawce.

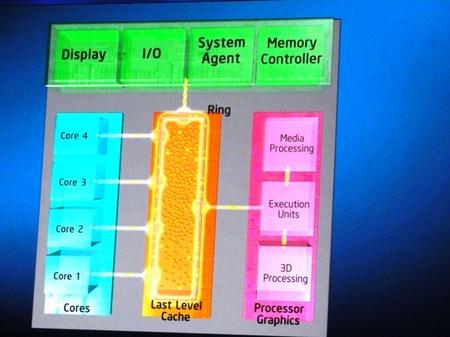

W architekturze Sandy Bridge układ graficzny staje się integralną częścią całego procesora - nie jest on umieszczony „obok” jak wcześniej, ale wewnątrz rdzenia w tym samym układzie krzemowym. Zmiany wprowadzone w układzie graficznym są jednak znacznie większe i poza samą integracją wewnątrz rdzenia mają również znaczący wpływ na jego wydajność, o czym dalej. Najpierw kilka słów o samych procesorach. Układy są produkowane w 32-nanometrowym wymiarze technologicznym i mają powierzchnię 225 mm2. Ich budowę przedstawia poniższy schemat:

Dla porównania schemat budowy 45-nanometrowych Core i7 z architekturą Nehalem:

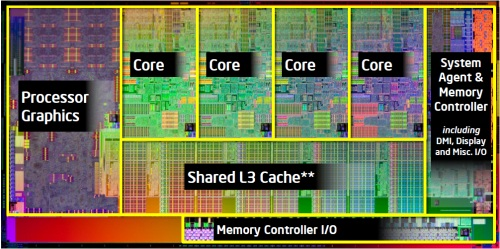

Porównując powyższe ilustracje łatwo zauważyć, że nowe procesory z architekturą Sandy Bridge stały się bardziej „podłużne”, a po obu stronach rdzeni i współdzielonej pamięci podręcznej przybyły nowe elementy. Kontroler pamięci, interfejsy wejścia/wyjścia i logika sterująca, które w układach Nehalem były umieszczone w różnych miejscach układu teraz znajdują się w jednej spójnej części nazwanej agentem systemowym (ang. system agent) widocznej na zdjęciu po prawej stronie. Po lewej natomiast pojawił się układ graficzny.

Sumarycznie nowe procesory składają się z trzech głównych części:

1) Części nadrzędnej (agenta systemowego) sterującej całym procesorem, zawierającej min. zintegrowany mostek północny, kontroler pamięci oraz kontrolery magistral PCI-Express i QPI/DMI

2) Części wykonawczej, a więc rdzeni x86 wraz z pamięcią podręczną trzeciego poziomu (w skrócie L3 lub LLC - Last Level Cache)

3) Zintegrowanego układu graficznego

Dodatkowo wszystkie z wymienionych modułów są w pewnym stopniu niezależne od siebie, gdyż zostały umieszczone w układzie i połączone ze sobą w taki sposób, że modyfikacja jednego z nich nie wymaga zmiany położenia lub przeprojektowania pozostałych. Dzięki takiej budowie, a głownie oddzieleniu od samych rdzeni i pamięci podręcznej L3 części nadrzędnej z kontrolerem pamięci i logiką odpowiedzialną za pracę całego układu Intel może łatwo modyfikować swoje nowe procesory, na przykład zwiększając lub zmniejszając liczbę dostępnych rdzeni.

Dla porównania procesory firmy AMD oraz dotychczasowe procesory Intela z architekturą Nehalem są podzielone na dwie części - część „core” składającą się z rdzeni x86 oraz część „un-core” zawierającą między innymi pamięć podręczną trzeciego poziomu i zintegrowany kontroler pamięci. W ich przypadku modyfikacja liczby rdzeni może sprawiać większą trudność niż w architekturze Sandy Bridge.

Modułowa budowa daje również duże możliwości w sferze zarządzania poborem energii procesora. Projektując nowe układy postanowiono to oczywiście wykorzystać - wszystkie trzy główne części procesorów Sandy Bridge są zasilane z oddzielnego źródła i taktowane własnym zegarem.

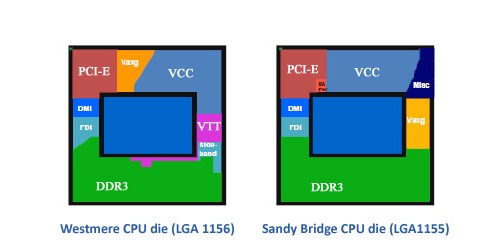

Najprawdopodobniej to nie kaprys Intela ale właśnie zmiany w sposobie zorganizowania i podziału wnętrza procesora wymusiły wprowadzenie nowej podstawki Socket LGA 1155, w miejsce dotychczas stosowanej LGA 1156 z którą zgodne są procesory z architekturą Nehalem. Obie podstawki różnią się tylko jednym pinem, teoretycznie więc mogły być ze sobą kompatybilne. Jak się jednak okazuje różnice nie dotyczą tylko jednego brakującego pinu, ale także pozostałych ze względu na zmiany w sposobie zasilania nowych procesorów. Podczas gdy układy z architekturą Nehalem były podzielone na dwie niezależne części, procesory z architekturą Sandy Bridge wymagają odrębnego napięcia dla trzech niezależnych części swojej struktury krzemowej. W efekcie zmianie uległo przeznaczenie części pinów w podstawce, co obrazuje poniższy schemat:

Poszczególne moduły są połączone ze sobą ze sobą za pomocą specjalnej magistrali pierścieniowej, która zapewnia płynną wymianę danych pomiędzy wszystkimi elementami procesora: rdzeniami x86, procesorem graficznym, pamięcią podręczną trzeciego poziomu oraz agentem systemowym i kontrolerem pamięci.

Idea zastosowania takiego rozwiązania jest bardzo prosta. W przypadku procesorów wielordzeniowych znaczący jest problem spójności danych - poszczególne rdzenie muszą utrzymywać identyczną zawartość swojej pamięci podręcznej. Do tego niezbędne jest wydajne połączenie pomiędzy rdzeniami - w przeciwnym wypadku następuje spadek wydajności całego procesora. Problem istniał w pierwszych generacjach układów dwurdzeniowych, jednak później rozwiązano go w układach z architekturą Core 2 Duo, wprowadzając współdzieloną pamięć podręczną drugiego poziomu, poprzez którą rdzenie wymieniały ze sobą informacje.

Pamięć podręczna również ma jednak swoje ograniczenia, polegające na ograniczonej przepustowości, stąd rozwiązanie okazało się niewystarczające dla układów 4-rdzeniowych. W efekcie w procesorach 4-rdzeniowych pojawiła się nowa trójpoziomowa struktura pamięci, w której jedna duża pamięć podręczna łącząca wszystkie rdzenie stała się pamięcią trzeciego poziomu, a każdy z rdzeni otrzymał dodatkowo własną pamięć podręczną drugiego poziomu. Takie rozwiązanie zmniejszyło częstotliwość odwołań do pamięci współdzielonej pomiędzy wszystkie rdzenie, pozwalając zachować odpowiednią wydajność połączenia.

W przypadku procesorów z architekturą Sandy Bridge w procesorze zintegrowany został układ graficzny, który również ma dostęp do współdzielonej pamięci podręcznej trzeciego poziomu. Dodatkowy element żądający dostępu do pamięci mógłby doprowadzić do tego, że powstałby w niej korek, niczym na skrzyżowaniu dróg równorzędnych. Postanowiono więc wprowadzić kontrolowany ruch okrężny, w postaci właśnie wspomnianej wcześniej magistrali pierścieniowej. Rozwiązanie jest już znane ze starszych układów graficznych R5xx/R6xx firmy ATI/AMD.

Pierścień w procesorach Sandy Bridge składa się w rzeczywistości z czterech niezależnych magistral - w tym 256-bitowego pierścienia danych oraz magistral żądań/potwierdzeń. Dane poruszają się wokół pierścienia z szybkością jednego przystanku na takt zegara. Przy częstotliwości taktowania 3,4 GHz wydajność pierścienia wynosi 96 GB/s na jeden przystanek. Ring jest na stałe zintegrowany w części wykonawczej procesora, a więc działa z częstotliwością taktowania charakterystyczną dla rdzeni procesora, niezależnie od taktowania zintegrowanego układu graficznego i agenta systemowego, a jego wydajność wzrasta po podniesieniu zegarów taktujących rdzenie.

Nowy układ graficzny

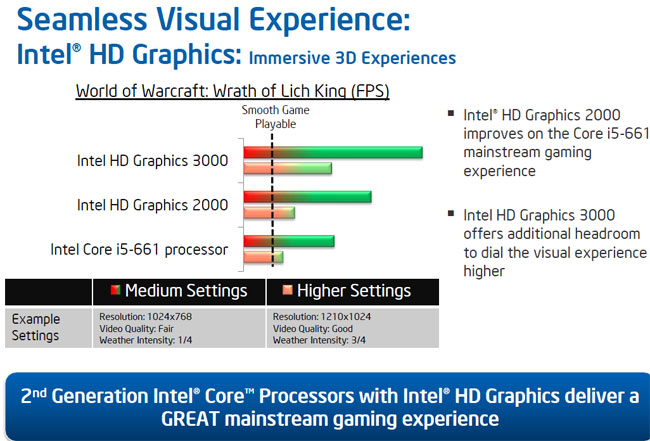

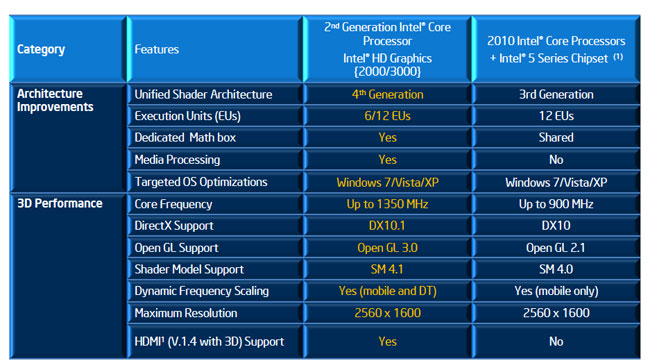

Układ graficzny procesorów Sandy Bridge składa się ze 114 milionów tranzystorów i jest sprzętowo zgodny z DirectX 10.1 oraz OpenGL 3.0. W sprzedaży dostępne będą procesory z dwiema wersjami układu - Intel HD Graphics 2000 z 6 jednostkami wykonawczymi, oraz Intel HD Graphics 3000 z 12 jednostkami.

Poza samą integracją wewnątrz procesora układ graficzny Sandy Bridge przeszedł także szereg poważnych zmian, dzięki którym ma oferować wyższą wydajność przetwarzania grafiki trójwymiarowej oraz akceleracji multimediów. Według Intela wydajność HD Graphics 2000 powinna być większa od oferowanej przez IGP instalowane w dotychczasowych procesorach z serii Westmere. Jeszcze lepiej ma być w przypadku HD Graphics 3000 z 12 jednostkami, który powinien oferować wydajność 2-krotne większą od dotychczasowych rozwiązań

Przejdźmy zatem do przedstawienie zmian, dzięki którym możliwy jest tak znaczący wzrost wydajności. Układ graficzny zintegrowany w Sandy Bridge (w wersji HD 3000) składa się z 12 jednostek wykonawczych. Ich liczba pozostała zatem niezmieniona w porównaniu do IGP starszej generacji z procesorów Westmere, ale każda z jednostek oferuje teraz dwukrotnie większą wydajność, co w prosty sposób powinno przełożyć się na wydajność całego IGP. Kolejną ze zmian jest możliwość korzystania z pamięci podręcznej trzeciego poziomu procesora - w efekcie spada częstotliwość bardziej czasochłonnego odwoływania się do pamięci operacyjnej komputera.

Oprócz tego znacznie wzrosły częstotliwości taktowania - nowy IGP może działać z zegarem do 1350 MHz, podczas gdy dotychczas było to maksymalnie 900 MHz.

Wprowadzone zmiany ze spokojem powinny wystarczyć na 2-krotny wzrost wydajności przetwarzania grafiki 3D, natomiast wydajność IGP w wersji HD 2000 z 6 jednostkami wykonawczymi nie powinna być gorsza niż starszych układów Intela.

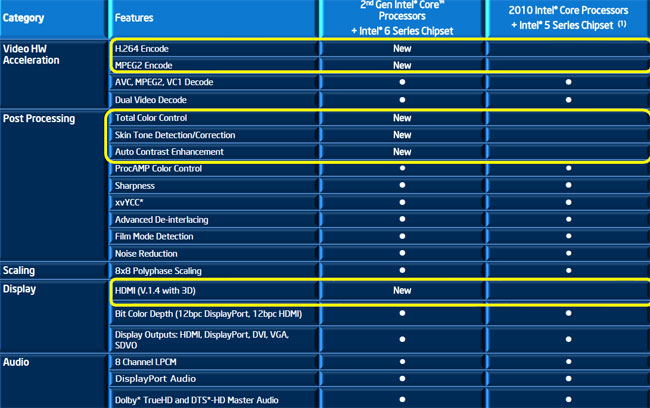

Intel nie poprzestał jednak tylko na usprawnieniach związanych z grami. Nowy układ graficzny zawiera szereg nowości adresowanych pod kątem mulltimediów. Elementy odpowiedzialne za wspomaganie odtwarzania materiałów wideo w wysokiej rozdzielczości zostały znacząco zmodyfikowane - układ graficzny procesorów Sandy Bridge jest w stanie dekodować równolegle dwa strumienie w rozdzielczości Full HD. Oprócz tego dodano sprzętowe wsparcie dla nowych formatów między innymi H.264 oraz technologię Quick Sync zapewniającą min. sprzętową akcelerację podczas kodowania wideo. Zmiany wprowadzone w nowym układzie graficznym pod kątem wsparcia multimediów są na tyle duże, że Intel określa swój nowy IGP nazwą "Procesor mediów i grafiki".

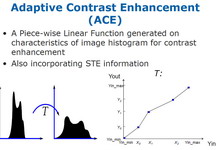

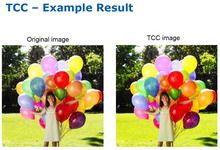

Co dla niektórych może być zaskoczeniem - zintegrowany układ graficzny Intel obsługuje złącze HDMI w wersji 1.4 oraz obraz stereoskopowy z częstotliwością odświeżania 120Hz. Funkcje te zostały dopiero niedawno wprowadzone w najnowszych kartach graficznych AMD i Nvidia. Podano dodano także trzy nowe rozwiązania, które poprawiają jakość obrazu w filmach: totalną kontrolę kolorów (tłumaczenie dosłowne, oryginał: Total Color Contror), detekcję oraz korekcję tonu twarzy (Skin Tone detection/correction) a także automatyczną poprawę kontrastu (Auto contrast enhancement).

Szczególnie ostatnia z tych nowości zasługuje na pochwałę - poprawa kontrastu następuje tutaj przez zabieg określany fachowo rozciągnięciem histogramu, a nie tylko przez "zwykłe" przyciemnienie ciemnych pikseli i rozjaśnienie tych już jaskrawych. Oznacza to, że rozwiązanie Intela nie zepsuje obrazu który już odznacza się wysokim kontrastem, natomiast znacznie poprawi jakość obrazu o niskim kontraście.

(kliknij, aby powiększyć)

Zmiany w architekturze rdzeni procesora oraz instrukcje AVX

W architekturze Sandy Bridge wprowadzono też szereg zmian w obrębie samych rdzeni. Dzięki nim nowe procesory mają odznaczać się wyższym wskaźnikiem IPC (Instructions Per Cycle), a co za tym idzie wyższą wydajnością w porównaniu do układów z architekturą Nehalem taktowanych takim samym zegarem. Według Intela poszczególne rdzenie Sandy Bridge oferują 10% wyższą wydajność "zegar-w-zegar" w porównaniu do rdzeni z architekturą Nehalem. Wskaźnik ten ma z biegiem czasu znacząco wzrosnąć, dzięki implementacji nowych instrukcji AVX.

Każdy rdzeń procesorów z architekturą Sandy Bridge (bez pamięci L2 i L3) składa się z 55 milionów tranzystorów i zajmuje powierzchnię 18,4 mm2. W porównaniu do poprzednich 32-nanometrowych procesorów z serii Westmere to o ponad jeden milimetr kwadratowy więcej. Szczegółowe porównanie rdzeni procesorów z architekturą Westmere/Nehalem i Sandy Brigde przedstawia poniższy rysunek:

Rdzeń Sandy Brigde jest tylko minimalnie większy od rdzenia Westmere - zmianie uległo natomiast rozmieszczenie poszczególnych elementów w jego wnętrzu, co świadczy o zmianach w architekturze.

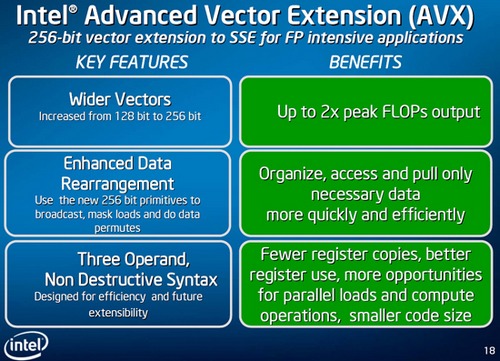

Najważniejszą z nowości w jest niewątpliwie implementacja instrukcji wektorowych Intel AVX (Advanced Vector Extensions). Sandy Bridge to pierwsze procesory, które obsługują nowy zestaw instrukcji.

Zadaniem AVX jest zwiększenie szybkości wykonywania obliczeń zmiennoprzecinkowych oraz strumieniowych. Umożliwić to mają 256-bitowe operacje zmiennoprzecinkowe, zwiększenie liczby operand z 2 do 3 oraz specjalne instrukcje wektorowe.

AVX ma znacznie zwiększyć wydajność części zmiennoprzecinkowej procesora, a także przyśpieszyć przetwarzanie mediów strumieniowych oraz wykonywanie zadań typowych dla środowiska HPC (High Performance Computing).

Zwiększenie liczby operand z 2 do 3 umożliwia łączenie aż 3 prostych instrukcji w jedną bardziej złożoną.

W celu umożliwienia wykonywania instrukcji AVX w jednostce zmiennoprzecinkowej Sandy Bridge zawarto 16 nowych 256-bitowych rejestrów YMM0-YMM15. W rzeczywistości stanowią one rozszerzenie dotychczasowych 128-bitowych rejestrów SSE (XMM0-XMM15).

256-bitowe operacje AVX stanowią największą od chwili debiutu procesorów Core 2 Duo w 2006 roku zmianę w części zmiennoprzecinkowej procesorów x86.

Jak każde nowe rozszerzenie zestawu instrukcji, także i AVX wymaga przystosowania oprogramowania. W chwili obecnej najprawdopodobniej żaden program nie jest jeszcze w stanie skorzystać z mocy drzemiącej w AVX i 256-bitowych operacjach zmiennoprzecinkowych. Z biegiem czasu i wraz z pojawieniem się aplikacji optymalizowanych pod kątem AVX wydajność procesorów z architekturą Sandy Bridge będzie wzrastać.

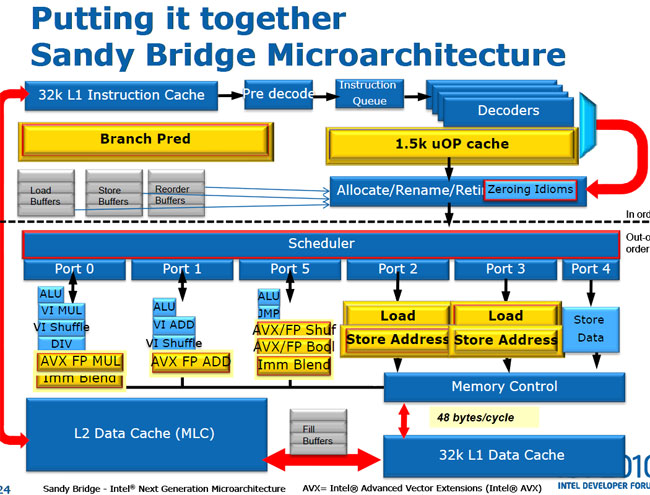

Poza implementacją instrukcji AVX w nowej architekturze wprowadzono także zmiany skutkujące wzrostem wskaźnika IPC (Instructions Per Cycle) a więc ogólnej wydajności przetwarzania instrukcji. Modyfikacje te nie są znaczące, jest ich jednak dość dużo, co przedstawia poniższy rysunek:

Kolorem żółtym i/lub czerwoną ramką zaznaczone zostały elementy nowe lub usprawnione. Zasadniczo architektura rdzeni Sandy Bridge nie różni się od wcześniejszej architektury Nehalem. Nowe procesory nadal mają 4-drożny dekoder rozkazów, stosowany od procesorów Core 2 Duo. System pobrań może dostarczyć do dekodera 16 bajtów danych na takt zegara, instrukcje przed wejściem do dekodera są w miarę możliwości łączone w paczki przez rozwiązanie Macro-op Fusion, a te już zdekodowane podlegają ponownemu sprawdzeniu i ewentualnie łączeniu poprzez bliźniacze rozwiązanie o nazwie Mico-op Fusion. Jest także sheduler, zajmujący się rozdzielaniem pomiędzy poszczególne jednostki wykonawcze zdekodowanych i gotowych do wykonywania instrukcji. Podobnie jak w procesorach Core 2 Duo i Nehalem ma on postać przystanku (w oryginale "reservation station"), w którym instrukcje oczekują na wykonanie. Również pamięć podręczna pierwszego poziomu dla instrukcji i dla danych ma rozmiar identyczny jak we wcześniejszych procesorach.

Istotną nowością wprowadzoną w architekturze Sandy Bridge jest dodatkowa pamięć podręczna, przechowująca zdekodowane instrukcje. Pamięć ta jest nazywana także przez Intela jako pamięć L0 i jest w stanie przechować około 1500 ostatnio zdekodowanych rozkazów. Dzięki temu w określonych sytuacjach wystarczy sięgnąć do jej zawartości, bez konieczności ponownego pobierania instrukcji z pamięci pierwszego poziomu i ich dekodowania.

Rozwiązanie może delikatnie zwiększyć wydajność oraz wpłynąć na zmniejszenie obciążenia dekodera rozkazów, który może zająć się pracą nad innymi instrukcjami lub... odpoczywać (tak jak na powyższym slajdzie), oszczędzając energię. Korzyści będą widoczne zwłaszcza w przypadku wykonywania przez procesor instrukcji często następujących po sobie - w tym przypadku nie trzeba ich ciągle "w kółko" dekodować, gdyż istnieje szansa, że już w zdekodowanej postaci znajdują się jeszcze w pamięci L0.

Warto dodać, że pamięć L0 nie jest fizycznie wbudowana w nowe procesory, lecz została wydzielona w części pamięci podręcznej pierwszego poziomu dla instrukcji. Kolejna ciekawostka - rozwiązanie tak naprawdę nie jest zupełnie nowe - podobna technologia była kiedyś stosowana przez Intela pod nazwą Trace Cache w procesorach Pentium 4, z tą różnicą, że wówczas pamięć ta miała dużo większą pojemność i całkowicie zastąpiła klasyczną pamięć podręczną pierwszego poziomu dla instrukcji.

Kolejną ze zmian w architekturze Sandy Bridge jest usprawniony system predykcji rozgałęzień. Nowy system predykcji jest w stanie równolegle śledzić więcej instrukcji, a ponadto dysponuje bardziej efektywnym sposobem przeglądania historii. Nie da się ukryć, że to właśnie możliwość sprawdzenia jak wcześniej zachowywała się dana instrukcja ma decydujący wpływ na skuteczność pracy systemu predykcji rozgałęzień, a tym samym wydajność całego procesora.

Usprawnienia zawarte w architekturze Sandy Bridge objęły ReOrder Buffer oraz sheduler, czyli dwie jednostki mające bezpośredni wpływ na stopień wykorzystania jednostek wykonawczych. ReOrder Buffer, odpowiedzialny za zmianę kolejności następujących po sobie instrukcji oraz ułożenie ich w taki sposób, aby można było wykonać jak najwięcej z nich jednocześnie ma teraz długość 168 pozycji, zamiast 128 jak w układach z architekturą Nehalem. Liczba wejść shedulera została natomiast powiększona z 36 do 54. Dzięki temu sheduler Sandy Bridge może przydzielić jednostkom wykonawczym instrukcje spośród większej niż dotychczas grupy, a więc wybrać w większym stopniu te, które można łatwiej wykonać równolegle.

Oprócz tego dodano nowy sposób, prostszy sposób zarządzania rejestrami, dzięki któremu poszczególne dane kopiowane są tylko raz, a ich lokalizacja (umiejscowienie w konkretnym rejestrze) nie może być zmienione przed dokonaniem obliczeń. Modyfikacja ta pozwala na zmniejszenie zużycia energii elektrycznej przez rdzenie procesora. Ponadto zwiększeniu uległa liczba buforów load/store.

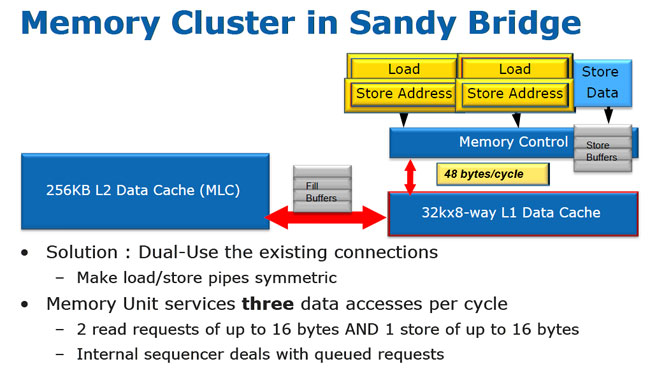

Twórcy architektury Sandy Bridge postanowili także wycisnąć więcej mocy ze zintegrowanego kontrolera pamięci. W architekturze Sandy Bridge część rdzenia odpowiedzialna za obsługę pamięci została rozbudowana - dzięki temu poszczególne rdzenie nowych procesorów w jednym takcie zegara mogą wysyłać trzy żądania dostępu do pamięci systemowej - dwa żądania odczytu (2x 16 bajtów) i jedno żądanie zapisu (1x16 bajtów). Dla porównania wcześniejsze układy z architekturą Nehalem mogły w jednym takcie wysyłać dwa żądania - jedno zapisu i jedno odczytu.

Takie zróżnicowanie liczby żądań odczytu i zapisu ma sens, gdyż procesor więcej pobiera z pamięci niż do niej zapisuje - pobierane są instrukcje oraz dane, natomiast zapisywane tylko dane, jako efekty wykonania na danych operacji określonych w konkretnych instrukcjach. W efekcie możliwość pobierania większej ilości danych z pamięci powinna skutkować również wzrostem szybkości zapisu do pamięci. Spoglądając na testy przepustowości pamięci tak rzeczywiście jest - zarówno prędkość zapisu jak i odczytu do pamięci RAM w procesorach z architekturą Sandy Bridge uległa niewielkiej, ale zauważalnej poprawie.

W nowej architekturze nie mogło również zabraknąć technologii HyperThreading znanej z wcześniejszych procesorów z architekturą Nehalem oraz instrukcji zapewniających sprzętowe wsparcie dla szyfrowania AES, które zostały wprowadzone przed rokiem w procesorach z serii Westmere. Oprócz tego niejako na dokładkę do instrukcji AES dodano również kilka specjalizowanych rozkazów, które mogą przydać się w specjalizowanych zastosowaniach takich jak np. kryptografia.

Turbo Boost 2.0

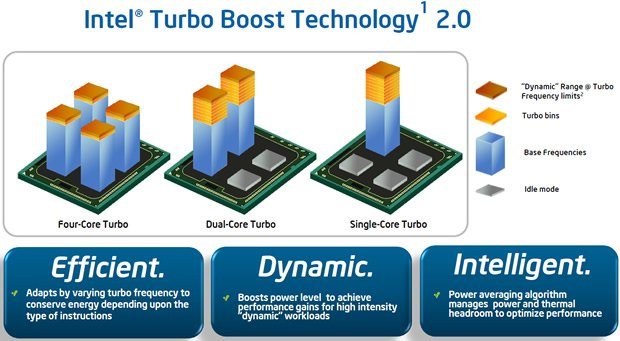

Zmiany wprowadzone w architekturze Sandy Bridge objęły również technologię Turbo Boost. Nowa wersja Turbo potrafi podkręcać nie tylko rdzenie procesora, ale również zintegrowany układ graficzny. To raczej naturalna zmiana wynikająca z integracji układu graficznego w tej samej strukturze krzemowej, a także zasilania go odrębnym napięciem zasilającym.

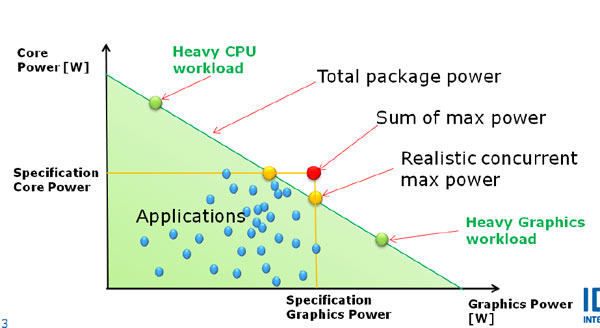

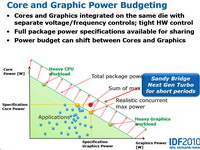

Turbo Boost 2.0 monitoruje obciążenie poszczególnych elementów procesora i na bieżąco reguluje ich częstotliwość taktowania. Taktowanie poszczególnych rdzeni tak jak w pierwszej wersji Turbo znanej z procesorów Nehalem zależny od ich aktywnej liczby - im mniej aktywnych rdzeni, tym większa częstotliwość taktowania pozostałych działających. Dla jednego aktywnego rdzenia częstotliwość zwiększana jest o 400 MHz natomiast dla czterech o 100 MHz. Tutaj nic się nie zmienia. Istotną zmianą jest natomiast zależność taktowania rdzeni od taktowania układu graficznego - w sytuacji dużego obciążenia GPU jego taktowanie jest zwiększanie, kosztem częstotliwości taktowania rdzeni procesora, i odwrotnie, co obrazuje wykres:

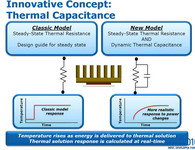

To jednak nie wszystko - Turbo Boost 2.0 zakłada również wykorzystanie pojemności cieplnej radiatora zainstalowanego na procesorze. W efekcie procesor który poprzednio pracował w trybie idle lub nie był znacząco obciążony, po wejściu w stan pełnego obciążenia może na krótko, na okres około minuty zwiększyć swoje taktowanie o dodatkowe 200 MHz, przekraczając limit TDP. Następnie po tym czasie taktowanie powraca do wartości maksymalnej określonej limitem wskaźnika TDP, a więc do poziomu do jakiego zwiększać częstotliwość może Turbo w pierwszej wersji z procesorów Nehalem. Ta zmiana może okazać się szczególnie przydatna, gdyż zapewnia przez moment dodatkową wydajność, która może być potrzebna, np. podczas ładowania gry czy nawet systemu operacyjnego. Szczegóły tej funkcjonalności przedstawiają poniższe sjaldy:

(kliknij, aby powiększyć)

Koniec łatwego taniego podkręcania

Wśród wielu zmian wprowadzonych w architekturze Sandy Bridge jest jeszcze jedna, o której warto wspomnieć. Wraz z nadejściem nowych procesorów kończy się era łatwego taniego nielimitowanego podkręcania. Podkręcanie procesorów Sandy Bridge jest bardzo łatwe, o ile jesteśmy w stanie za to dopłacić - w przeciwnym wypadku łatwo na pewno nie będzie.

W zasadzie jedyną możliwością podkręcania nowych procesorów jest zmiana (zwiększenie) mnożnika. Podkręcanie poprzez magistralę QPI tak jak w procesorach Nehalem nie jest już możliwe. W nowej architekturze częstotliwość QPI jest na stałe powiązana z częstotliwością innych magistral, takich jak np. PCI-Express. W efekcie jej zwiększenie jest możliwe tylko o kilka procent. Zatem sumarycznie poprzez zwiększenie częstotliwości QPI można uzyskać zaledwie około 100 MHz, a to przy częstotliwości taktowania procesora wynoszącej około 3 GHz z pewnością nie jest wartością dającą satysfakcję.

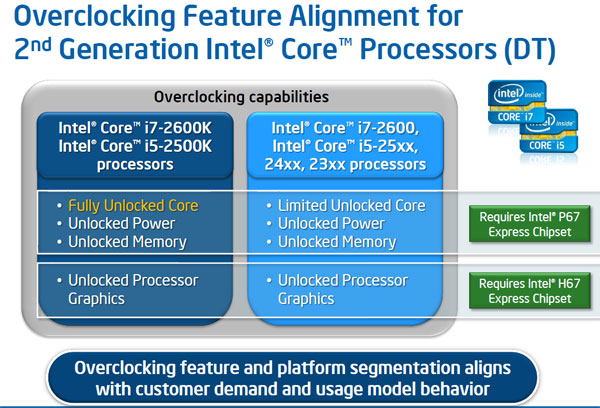

Dla osób które lubią podkręcać Intel przygotował specjalne wersje procesorów z odblokowanym mnożnikiem: Core i7 2600K oraz Core i5 2500K. Niestety są one odpowiednio droższe w porównaniu do analogicznych układów z zablokowanym mnożnikiem. Dla niektórych może to być wydatek zbyt wysoki. Pozostałym pozostają jedynie "ograniczone" możliwości podkręcania w postaci możliwości zwiększania bazowego mnożnika o maksymalnie 4, a więc częstotliwości taktowania procesora o nie więcej niż 400 MHz. W dodatku taka możliwość będzie istniała jednak tylko w przypadku, gdy procesor z architekturą Sandy Bridge zainstalujemy w płycie z chipsetem P67.

Jeżeli zechcemy skorzystać z układu graficznego zintegrowanego w nowych układach, będziemy musieli wybrać płytę z chipsetem H65 lub H67, w których powyższa możliwość nie będzie dostępna.

Na pocieszenie Intel przygotował aplikację Extreme Tuning Utility, która w zamyśle ma ułatwić nadzorowanie pracy Turbo 2.0 i modyfikowane parametrów pracy układów.

|