|

TwojePC.pl © 2001 - 2024

|

|

RECENZJE | Test: Pentium 4 Prescott na tle innych |

|

| |

|

Test: Pentium 4 Prescott na tle innych

Autor: Lancer | Data: 03/03/04

|

Przed niespełna miesiącem, Intel oficjalnie przedstawił zapowiadane od długiego czasu jądro, mające wnieść świeży powiew w starzejącą się linię procesorów Pentium 4 Northwood. Pojawił się Prescott. Chip nadal oficjalnie zaliczany do czwartej generacji procesorów Pentium. Na temat samego układu powstało wiele mitów i to na długo przed premierą. Część plotek wydawała się mało wiarygodna, zaskakując rozbudowaną historyjką, część mogła być bliska prawdy. Niewiele jednak było wiadomo oficjalnie. Dziś nasza znajomość tajników Prescotta wskazuje, że nie jest on prostu ulepszonym Northwoodem. Procesor wnosi nową jakość. To chip, który będzie głównym produktem handlowym Intela na najbliższe miesiące. Przed niespełna miesiącem, Intel oficjalnie przedstawił zapowiadane od długiego czasu jądro, mające wnieść świeży powiew w starzejącą się linię procesorów Pentium 4 Northwood. Pojawił się Prescott. Chip nadal oficjalnie zaliczany do czwartej generacji procesorów Pentium. Na temat samego układu powstało wiele mitów i to na długo przed premierą. Część plotek wydawała się mało wiarygodna, zaskakując rozbudowaną historyjką, część mogła być bliska prawdy. Niewiele jednak było wiadomo oficjalnie. Dziś nasza znajomość tajników Prescotta wskazuje, że nie jest on prostu ulepszonym Northwoodem. Procesor wnosi nową jakość. To chip, który będzie głównym produktem handlowym Intela na najbliższe miesiące.

Niniejszy artykuł przybliżający tajniki Prescotta składa się z dwóch części. Część teoretyczną stanowi opis zmian poczynionych przez inżynierów w najnowszym jądrze w stosunku do układów starszych i dobrze znanych. Ponieważ teoria zawsze w jakiejś części zbiega się z praktyką, więc nie zabrakło testów wydajnościowych Prescotta, mających dać dowód skuteczności wprowadzonych ulepszeń. By oddać pełnię możliwości nowego rdzenia, testom poddał się nie tylko nowy Pentium, ale także jego poprzednicy ze stajni Intela, oraz bezpośredni rywale z obozu AMD. Zapraszam na bliskie spotkanie z procesorami Prescott. | |

|

Prescotta czas poznać

O nowym układzie było głośno już jakiś czas temu. Miał ukazać się nim śnieg spadnie, ale nie było go do teraz. W końcu jednak pojawił się..... i rozczarował. Wszyscy sądzili, że będzie szybszy od starszych układów. A tymczasem...

W nowym jądrze Intel zastosował najwięcej nowości od czasu debiutu innowacyjnego P4 Wilamette. Northwooda wyróżniał jedynie 0,13um proces wykonania, podwojona pojemność cache L2 oraz odblokowany z czasem HT i przyspieszona szyna FSB. Prescotta dotknęły ogólnie podobne, ale głębiej sięgające zmiany.

Najważniejszą nowinką, dającą podstawę do kolejnych ingerencji w konstrukcję jądra jest przeniesienie procesu produkcyjnego z wymiaru 0,13um na 0,09um. Przy tej okazji pojawiły się dwie nowości. Użyto technologii Strained Silicon - rozciągniętego krzemu i zastosowano nowy, 7 warstwowy materiał izolacyjny o obniżonej stałej dielektrycznej low-k CDO (Carbon Doped Oxide). Zasada funkcjonowania Strained Silicon opiera się na rozrzedzeniu atomów krzemu w celu ułatwienia przepływu elektronów w tranzystorach. Wraz ze spadkiem "oporu" rośnie bowiem szybkość przepływu elektronów - nawet rzędu 20%. To z kolei pozwala na sprawniejszą komunikację jednostek logicznych. Elektryczne połączenia wewnętrzne, podobnie jak przy wcześniejszym 0,13um procesie wykonano przy użyciu miedzianych ścieżek. Zastosowanie izolatora o niższej stałej dielektrycznej (CDO) w miejsce używanego do tej pory SIOF pozwala m.in. obniżyć poziom napięć zasilających.

Niższy proces technologiczny ma trzy podstawowe zalety. Im mniejszy wymiar, tym mniejsze jednostki jądra procesora w stosunku do tych, wykonanych we wcześniejszej technologii. Im mniejszy układ, tym więcej przyszłych procesorów można wytrawić na powierzchni jednego krążka wafla krzemowego. Intel korzystając z 30cm wafli zyskuje dodatkowo. Powierzchnia tradycyjnego 20cm krążka krzemowego jest ponad dwukrotnie mniejsza od nowego 30cm. Korzystający ze starszych technik ma do dyspozycji mniejszą powierzchnię użytkową. O ile na 30cm waflu jest to 2826cm^2, to 20cm ma powierzchnię już tylko 1250cm^2. Zysk ekonomiczny jest nie do przecenienia. No i co najważniejsze - niższy wymiar pozwala zwiększyć częstotliwość pracy tranzystora, czyli najmniejszej jednostki składowej procesora. Ostatecznie więc Prescott powinien bez problemów pracować z zegarami nieosiągalnymi dla wcześniejszych konstrukcji. Trzecią cechą, jest zmniejszona emisja cieplna. Cóż ta ostatnia, jak się przekonamy w dalszej części Prescotta raczej nie charakteryzuje...

Na poniższym zdjęciu widzimy rentgenowskie ujęcia Northwooda i Prescotta. Nasz główny bohater, mimo iż powinien być sporo mniejszy, to jednak znacząco nie stracił wymiarowo. O ile stary Northwood ma powierzchnię 127mm^2, to u Prescott jest to aż 112mm^2. Skąd taka "niewielka" różnica? Może inne dane nieco lepiej przemówią. O ile Northwood zbudowany jest z 55mln tranzystorów, to nowy układ już ze 125mln. Prawda że wygląda imponująco? Skąd się wzięły dodatkowe tranzystory?

Struktura Northwooda i Prescotta

Dużą część powierzchni nowego procesora pochłania powiększona pamięć podręczna. 1024KB całkowitej pojemności cache L2, jaką dysponuje Prescott to dwukrotność tego czym dysponuje Northwood i aż czterokrotnie więcej niż u Willamette. Wielkość to jednak nie wszystko. Co prawda nadal jest to pamięć typu skojarzeniowego z identyczną ośmiodrożną, 256bitową ścieżką dostępu, to jednak posiada ona dłuży czas dostępu i jest przez to wolniejsza. O ile u Northwooda opóźnienie cache L2 to około 18cykli, to u Prescotta dochodzi już do 30cykli. Wysoka latencja może mieć duży wpływ na wydajność.

Podobnie jak cache L2, tak też pamięć podręczna poziomu pierwszego zwiększyła swą pojemność. Dotychczasowe 8KB przeznaczone na instrukcje rozrosło się do 16KB. Niestety i w tym wypadku Inetel wydłużył czasu dostępu z 2 do 4 cykli. Niezmieniona pozostała charakterystyczna tylko dla architektury NetBurst pamięć Trace Cache L1. Ma ona nadal pojemność 12tys mikrooperacji.

0,09um proces technologiczny sprzyja powiększeniu rozmiarów pamięci. Jest możliwe dzięki spadkowi wymiarów pojedynczej komórka SRAM. O ile u 0,13um Northwooda były to 2u^ 2, w 0,09um są to tylko 1,15u^ 2.

Kolejna istotna różnica - wydłużony potok wykonawczy. Wyjątkowo długi, bo liczący 20 stopni potok wydłużył się do 31 etapów. To zupełnie niespotykane w rozwiązaniach konkurencji zagranie. Co prawda im dłuższy potok, tym każdy jego pojedynczy etap jest mniej obciążony, a jednostki nań się składające mogą być prostsze i sumarycznie układ taki może pracować z wyższym zegarem, to jednak taka konstrukcja nie pozostaje bez wad. W porównaniu zegar do zegara, układ z długim potokiem wykonawczym jest mniej wydajny, spada współczynnik IPC (Instructions Per Clock - ilość wykonywanych instrukcji przeliczona na jeden takt zegara). Niewątpliwą wadą takiej konstrukcji jest bardzo duża czułość na skoki instrukcji programu. W niektórych przypadkach może się bowiem zdarzyć, że pewna operacja, która jest praktycznie na ukończeniu (znajduje się na końcu potoku) musi skorzystać z danych wcześniej nie przetworzonych, a istotnych z punktu widzenia prawidłowego wykonania całego zadania. Układ musi przerwać pracę i zaczynać całą pracę od nowa z konieczności odwołania się czynności wcześniej nie przewidzianej. Na tym etapie pojawia się ogromna strata czasu, spowodowana potrzebą powtórnego zapełniania jednostek bardzo długiego potoku, a procesor musi od nowa wszystko zaczynać. Aby temu przeciwdziałać Pentium 4 od początku wyposażono w cały wachlarz przeciwśrodków, jak np. pamięć Trace Cache L1.

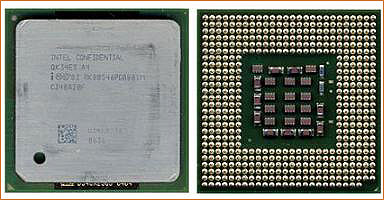

Pentium 4 E w całej okazałości (wersja inżynieryjna).

Procesor fizycznie niewiele się różni od Northwooda

Obecne od samego początku architektury NetBurst jednostki pobrań wyprzedzających i predykcji rozgałęzień programu (PreFetch & BranchPrediction) są bardzo ważne dla Prescotta. Uchodzące za wyjątkowo skuteczne, mechanizmy zostały jeszcze udoskonalone w stosunku do tej znanej z Northwooda. Zmiany objęły wprowadzenie poprawionych algorytmów odpowiedzialnych za pre-odczyt i poprawiające skuteczność trafień nadchodzących odgałęzień programu. Całość układu odpowiedzialna jest za przewidywanie skoków instrukcji programu i pobieranie zawczasu danych potrzebnych jednostkom wykonawczym w następnej kolejności. Właśnie działanie pre-odczytu jest jedną z przyczyn powiększenia pamięci podręcznej. Cache przechowuje dane uzyskane przez jednostkę pobrań wyprzedzających, a dużo wyższa od pamięci RAM przepustowość pamięci podręcznej pozwala na szybszy dostęp do danych, które w ekstremalnym przypadku mogą okazać się niezbędne dla zapełnienia jednostek bardzo długiego potoku wykonawczego.

Nowością jest rozszerzenie znanych jeszcze z Willamette listy 144 rozkazów SIMD SSE2 o 13 nowych instrukcji nazwanych początkowo PNI (Prescott New Instruction), a teraz znanych jako SSE3. Poszczególne rozszerzenia to:

- fisttp: instrukcja odpowiedzialna za konwersję liczby zmiennoprzecinkowych na stałoprzecinkowe

- addsubps, addsubpd, movsldup, movshdup, movddup: działania na liczbach złożonych

- lddqu: procesy kompresji video

- haddps, hsubps, haddpd, hsubpd: grafika przestrzenna

- monitor, mwait: synchronizacja wątków w ramach HyperThreadingu

Promowana przez Intela technologia HyperThreading (współbieżności wielowątkowej) została poddana delikatnej modyfikacji. Oprócz dodania dwóch wspomnianych już instrukcji SSE3 odnoszących się do HT i kilku pomniejszych zmian, rozszerzono zakres operacji mogących być wykonywanych jednocześnie z 24 do 32. Zwiększono liczbę buforów śledzących wątki z 6 do 8. Na skuteczność pracy w środowisku wielowątkowym wpływa też uskutecznienie działań jednostki pobrań wyprzedzających i predykcji rozgałęzień programu.

Zupełną niespodzianką jest poszerzona szyna adresowa procesora. Ma ona aż 40 bitów. Dzięki temu rozwiązaniu ulepszony Pentium 4 jest w stanie adresować do 1024GB pamięci. Dotychczas stosowana 32-bitowa szyna zapewniała obsługę tylko do 4 GB pamięci. Jest to o tyle ciekawe, że identyczną przestrzeń oferuje 64-bitowy Athlon 64. Taka zmiana jest oczywistym ukłonem ku serwerowym odmianom Procesora, zapowiadanym na najbliższą przyszłość.

Prescott od samego początku jest przygotowany na kolejną rozbudowę. Inżynierowie wyposażyli jądro w szynę Back Side Bus (BSB) umożliwiającą proste przyłączenie pamięci cache L3. Rozwiązanie to pozwoli bardzo prosto stworzyć wydajne chipy serwerowe, jak i biurkowe demony wydajności w stylu P4 EE/Xeon Gallatin.

Ostatnią wartą wspomnienia zmianą jest umożliwienie mnożenia całkowitoliczbowego przez jednostki ALU. To może znacząco usprawnić działanie, biorąc pod uwagę fakt, że do tej pory tego typu operacjami zajmowały się jednostki zmiennoprzecinkowe.

Zmodyfikowany procesor na chwilę obecną pracuje w gnieździe socket 478, jest pinowo zgodny z dotychczasowymi układami Northwood. Zadebiutowały do tej pory dwie rodziny Prescottów. Najsłabsze są układy oznaczone jako Pentium 4 2,4 A i 2,8GHz A. Pracują one z FSB 533MHz i mają wyłączony HyperThreading. Przeznaczone są do pracy ze starszymi płytami opartymi o chipsety bez wsparcia dla HT i FSB800MHz, bowiem kolejne, wydajniejsze układy pracują już na szybszej szynie - 800MHz. Mają także aktywny HyperThreading. Taktowane są zegarami 2,8GHz i 3GHz. Cała ta czwórka zasilana jest napięciem od 1,25 do 1,4V przy natężeniu 78A. Ich TDP (Thermal Design Power) wynosi 89W. Najsilniejszymi dostępnymi układami są Prescotty taktowane zegarami: 3,2GHz i 3,4GHz. Posiadają oczywiście aktywny HyperThreading i pracują z 800MHz FSB. Ich TDP to już 103W. Zasilane napięciem 1,25-1,4V przy natężeniu 91A. Pentium 4 E taktowany zegarem 3,4GHz, nie jest on jednak jeszcze dostępny w sprzedaży detalicznej. Prawdopodobnie z uwagi na kłopoty produkcyjne wprowadzenie na rynek przesunięto na marzec tego roku. Wszystkie Pentium 4 Prescott z FSB 800MHz i HT dla odróżnienia od poprzednich Pentium 4 C zbudowanych na jądrze Northwood oznaczane są literką E. Układy bez HT i FSB 533MHz dostały literkę A. Sumarycznie mamy więc na rynku 6 nowych procesorów - P4: 2,4GHz A, 2,8GHz A, 2,8GHz E, 3GHz E, 3,2GHz E i czekający w kolejce P4 3,4GHz E.

Na koniec przyjrzyjmy się tabelce. Ilustruje ona złożoność jądra z podziałem na "czysty" rdzeń i tranzystory składające się na pamięć podręczną. Ich ilość jednak zupełnie nie odpowiada zmianom poczynionym w jądrze układu. Prescott składa się ze 125mln tranzystorów. O ile w przypadku Northwoda pamięć podręczna stanowiła niemal połowę powierzchni układu, tu takiego podziału nie można dokonać. Wymiary samego jądra wzrosły ponad miarę. Wydłużony potok i kilka innych zmian zupełnie nie tłumaczy takiego zjawiska. Chip powiększył się dwu i półkrotnie!

Zupełnie niedawno Intel wyjawił część tajemnicy. Jądro Prescotta kryje w sobie technologię nazwaną Clackamas Technology. Pozwala ona na sprawne wykonywanie 32 i 64-bitowego kodu zgodnego z x86, a więc kompatybilnego z rozszerzeniem AMD64. Prescott na zdjęciach rentgenowskich wyraźnie pokazuje co ma w sobie. Okazuje się, że wspomniana wcześniej ulepszona jednostka ALU została rozbudowana, a dokładniej podwojona. Tak! Prescott ma dwie jednostki ALU, które po połączeniu zapewniają pracę w trybie 64-bitowym. Parkę tą nazwano Arithmetic Logic Links (w bardzo ładnym skrócie - ALUMINUM). Intel wspomina, że potrafi ona pracować w dwóch trybach: 32-bitowym z częstotliwością 7GHz (ALU w Pentium 4 zawsze pracowało z podwójnym zegarem procesora), zaś tryb 64-bitowy, kiedy taktowanie wynosi 4GHz potrafi zwiększyć wydajność o 20% przy jednoczesnej redukcji emisji ciepła.

Prescott z uwidoczniony ALUMINUM (kliknij, aby powiększyć)

Na tym jednak dobre wiadomości się kończą. Na razie CT zostało zarezerwowane dla pracujących w parach serwerowych chipów Nocona oraz jednoprocesorowych Prescottów przeznaczonych jednak nie do komputerów biurkowych, a serwerów/stacji roboczych. Pod strzechy CT zawita dopiero za rok, wraz z nadejściem Tejasa - procesora opartego o jądro Prescott, wykonanego w 0,065um procesie technologicznym z 2MB cache L2 i 24KB cache L1, i 16tys uOps, oraz rozszerzeniem SSE4, na razie znanym jako TNI. Intel każe więc "pospólstwu" czekać z 64-bitami do chwili rozpowszechnienia się stosownego oprogramowania. Wtedy dopiero domowy P4 popracuje w nowym środowisku.

|

|

|

|

|

|

|

|

|

|